https://core.ewha.ac.kr/publicview/C0101020140429132440045277?vmode=f

반효경 [운영체제] 19. Memory Management 2

설명이 없습니다.

core.ewha.ac.kr

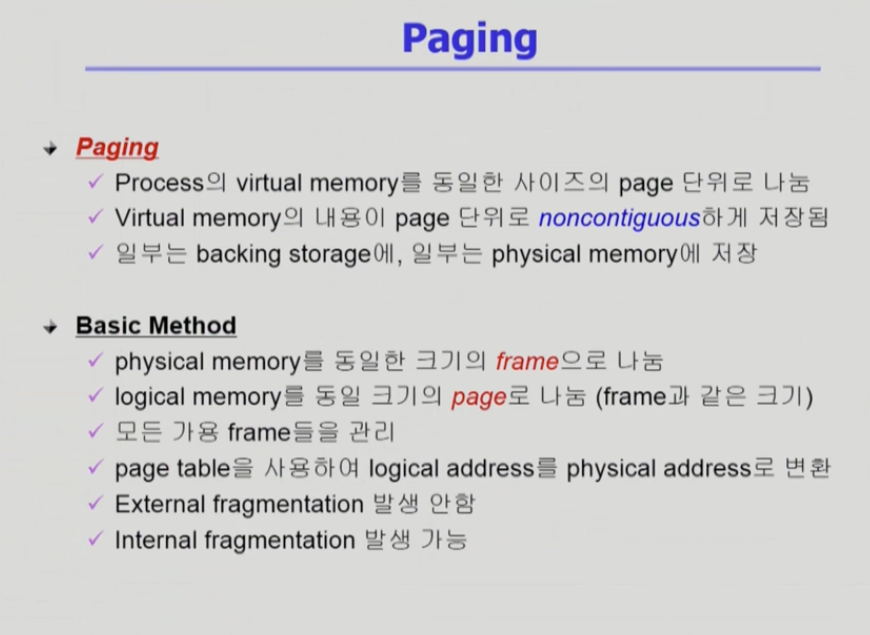

물리적인 메모리 관리 기법중 불연속적 할당중 paging 부터 살펴볼것이다.

우선 주소 변환(바인딩) 이 기존의 간단하게 두개의 레지스터로 하는방법은 더이상 사용할수 없음

-> 어디에 어떻게 페이지들이 올라가있는지 파악해야함

프로그램을 구성하는 논리적인 메모리를 동일한 크기의 페이지로 잘라서 각각의 페이지를 물리적 메모리의 적당한위치(비어있다면 어디든) 올라갈수 있게해주는 기법이다.

페이징에서 주소 변환(바인딩)을 하기위해 page table 라는것이 사용된다.

page tabel 은 각각의 논리적인 페이지들이 물리적인 메모리 어디에 올라가있는지 표시되어있는것이다.

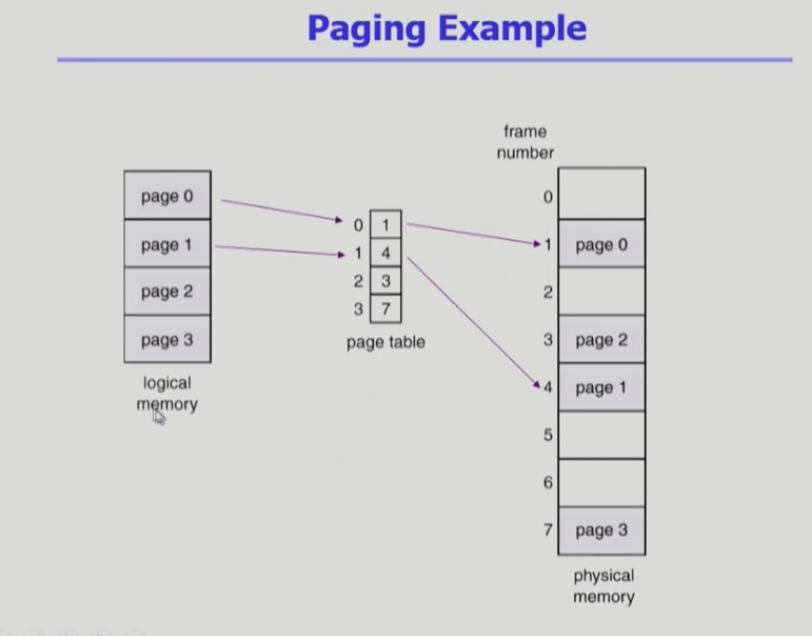

그림의 예시를보면 페이지 테이블에 로지컬 메모리 번호별로 실제 메모리 주소값(프레임 번호)이 들어있는 테이블이있다.

페이지 테이블은 논리적인 페이지의 페이지수 만큼 엔트리가 존재하게된다.

테이블이 한마디로 배열이다. -> 접근할때 순차적으로 다검사할 필요가 없음 index 를 통해서 바로접근

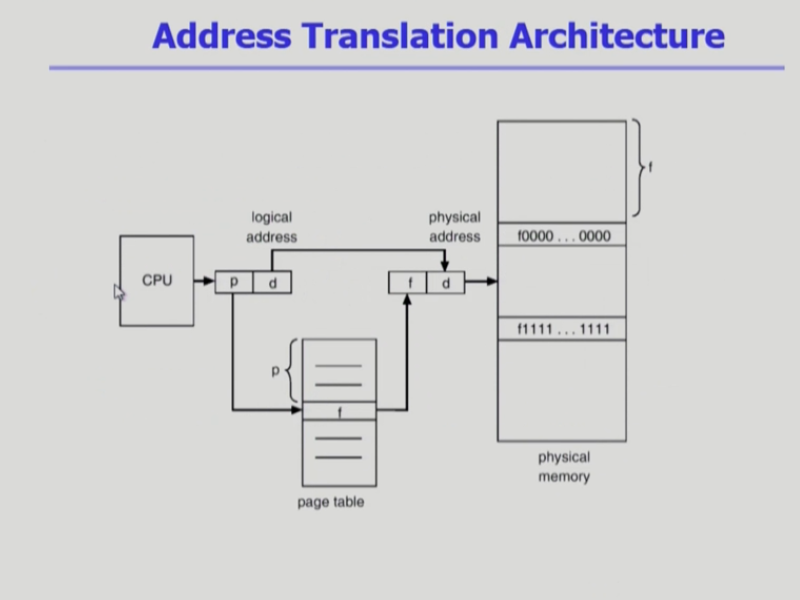

page table 을 이용하는 방법을 좀더 자세히 표현한 자료인데

d가 offset page로 부터 얼마나 떨어져있느냐라는데 -> 페이지가 경기도면 offset은 나머지 세부주소이다(금곡동 어쩌구저쩌구)

-> 주소 변환이 일어나도 logical address 의 offset과 실제 메모리 offset은 안바뀐다.

어쩃든 cpu가 logical address 를 주면서 메모리가져오라고 하면

이제 페이지 테이블을 통해 실제 물리적메모리 위치가 어딘지 파악하고 그것통해 메모리 내용을 가져오는것이다.

페이지 테이블은 어디에 위치해야하는가?

페이지의 단위는 대부분 4kb이다. -> 한 프로그램 100만개 정도로 짤린다 100만개의 엔트리를 가진 테이블을 cpu의 레지스터에 들어갈수 있는가? -> 못들어간다 용량이 너무 크다

그리고 테이블은 각 프로그램별로 별도로 존재해야한다.

그래서 페이지 테이블은 메모리에 들어가게 된다.

메모리를 접근하기 위해선 페이지 테이블에 접근해야하고 페이지 테이블이 메모리에 존재하기 때문에

메모리접근을 위해선 메모리 접근이 두번 일어나야한다.

메모리 테이블을 위한 접근, 메모리를 실제적으로 가져오기위한 접근

이제 MMU에서는 기존에 base register 랑 limit register 있었던게

page table base register 랑 page table length register 이 대용으로 사용된다.

똑같이 시작점인데 -> page table 에 있는 page 시작점과 page 의 크기를 가지고있는것이다.

메모리를 접근하려면 2번의 메모리 접근이 필요하다고 했다

-> 상당히 비용이 크다

속도향상을 위해 별도의 하드웨어를 사용한다

-> associative register 로 구성되는 TLB 라는 일종의 캐시이다.

메인메모리보다 빠른 주소변환을 위한 계층이다

메인메모리 보다 빠른 캐시 메모리(운영체제 입장에서는 감추어진 계층이다 컴퓨터 구조적인 측면에서만 바라봄) TLB 를 운용하여 page table 의 일부를 가지고있는 것이다(빈번하게 불리는 것들만 가지고 있는것이다).

당연히 캐시니 메모리에있는 페이지 테이블에 접근하기 이전에 TLB에 우선 접근후 메모리에 접근하는 방식이다.

TLB 는 p 즉 프로그램 시작점부터 얼마나 떨어져있는지 알수가없음 모든 정보 가지고있는것이 아니니(자료 참고)

그래서 p에 대한 값들도 가지고있어야함(page number) 그리고 그에 대응하는값 frame number를 갖고있는것이다.

TLB 는 전체를 다 검색하게 된다 있는지 없는지 모르니까 전체 탐색을 하게될것이다.

전체 탐색이 오래걸리니 병렬적으로 탐색할수있는 associative register 로 되어있음

페이지 테이블은 각 프로세스별로 존재함 -> TLB 도 각 프로세스 마다 다 다를것이다.

컨텍스트 스위칭이 일어날떄마다 flush가 일어나서 다 한번 캐시를 쫙 지운다.

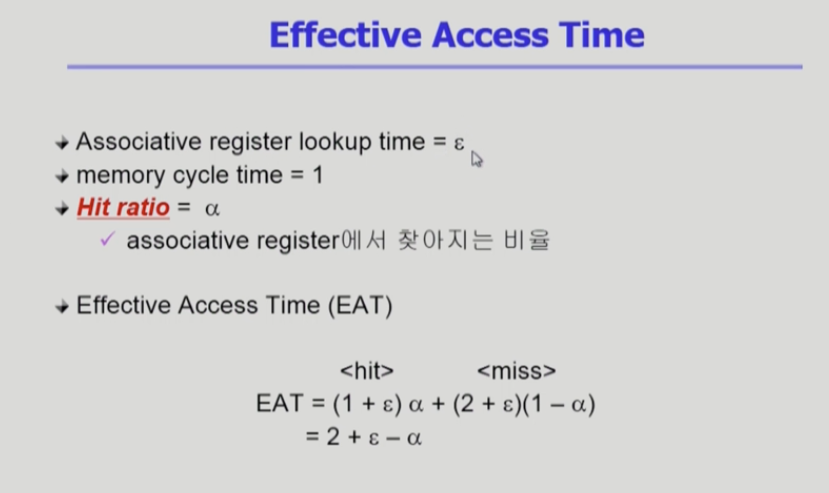

실제로 메모리 접근하는 시간의 식인데 이정도까지는 외우기는 애매하다 넘기자

2단계 페이지 테이블

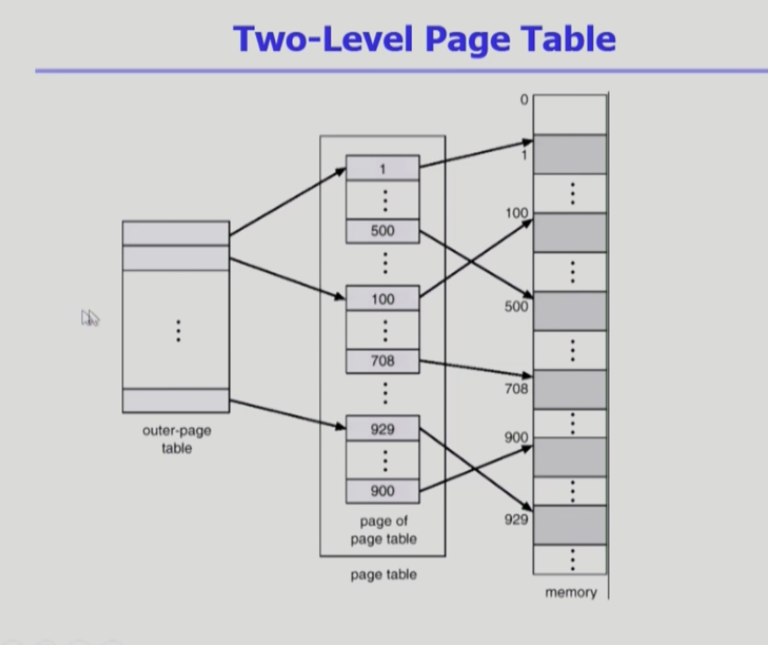

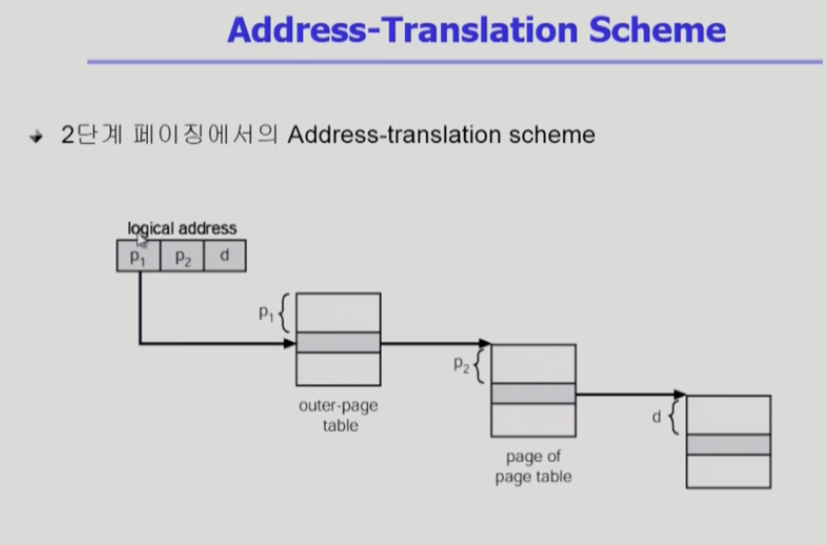

2단계 페이지 테이블은 자료에 보이는것처럼 안쪽 페이지 테이블과 바깥쪽 페이지 테이블이있어서 cpu가 논리적 주소를 주면 페이지 테이블을 두번 거쳐서 주소를 변환하여 메모리에 접근한다.

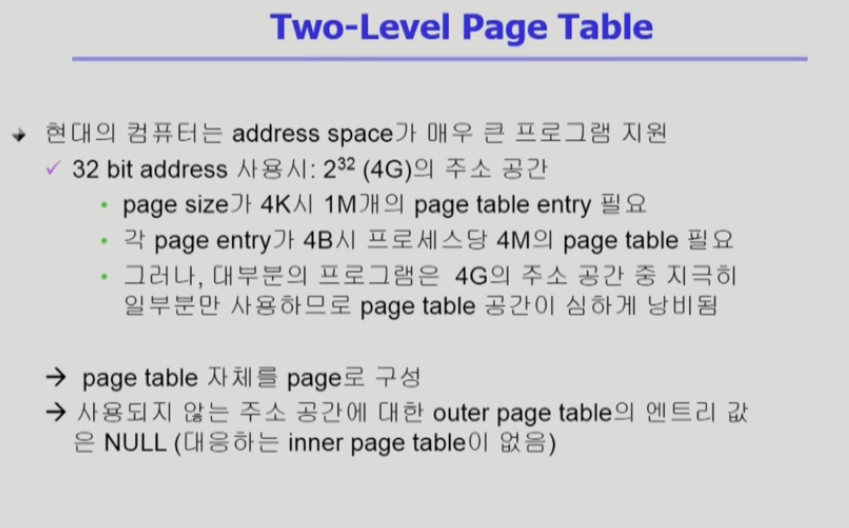

2단계 왜사용하는가?

-> 페이지 테이블을 위한 공간을 줄이기 위해서 사용한다.

->중간에 안사용하는 부분 내부 테이블 부분에서 안만들고 생략한다. 그래서 공간을 줄일수 있다.

현대의 컴퓨터에서는 메모리 주소 체계가 굉장히 크다 -> 요즘 64비트 주소 체계니까 logical address 한조각이 64비트인 것이다.

일단 자료에서는 32비트로 설명한다.

32비트로 표현할수있는 논리적인 주소의 한계는 ->2^32 개이다.(프로그램의 크기)

프로그램을 구성하는 버츄얼 메모리의 크기의 결정은 주소체계를 몇비트의 주소체계를 쓰는가에 달렸다.

메모리의 주소는 바이트 단위로 매겨진다

여기 0~ 3000 까지있는게 1줄이 바이트 이다 0 == 0번째 바이트

2^32 가 4기가 이고 거기에 바이트 단위라 4기가 바이트이다.

2^10 = 킬로 2^20 = 메가 2^30 = 기가 이렇게 불린다.

4기가 바이트 단위로 되어있는 버츄얼 메모리를 페이지로 쪼개는것인데

각 페이지의 크기가 4kb라고 하였다 -> 2^20 즉 1메가개의 페이지 수가 나온다.

페이지의 엔트리가 1메가개 즉 100만개 이상의 엔트리가 나온다.(크기가 큼)

이게 각 프로그램마다 페이지 테이블이 따로있는데 -> 메모리에 들어가야하는데 공간낭비가 심해짐

각 페이지 테이블이 4바이트 정도된다. -> 프로세스당 4M바이트의 페이지 테이블이 필요하다.

즉 그냥 페이지테이블 그대로 넣으면 공간 많이 차지하니 2단계 페이지 테이블을 사용한다.

그리고 로지컬 메모리 자체 4gb의 공간중 막상 프로그램이 운영하는 부분은 극히 일부분이다. -> 더 비효율적이게 됨

저기 로지컬 메모리에 코드,데이터,스택이 들어가는데 중간에 안쓰는 빈부분이 분명 있을것이다.

게다가 안쓰는 부분이라고 페이지를 안만들수없다 페이징기법에서는

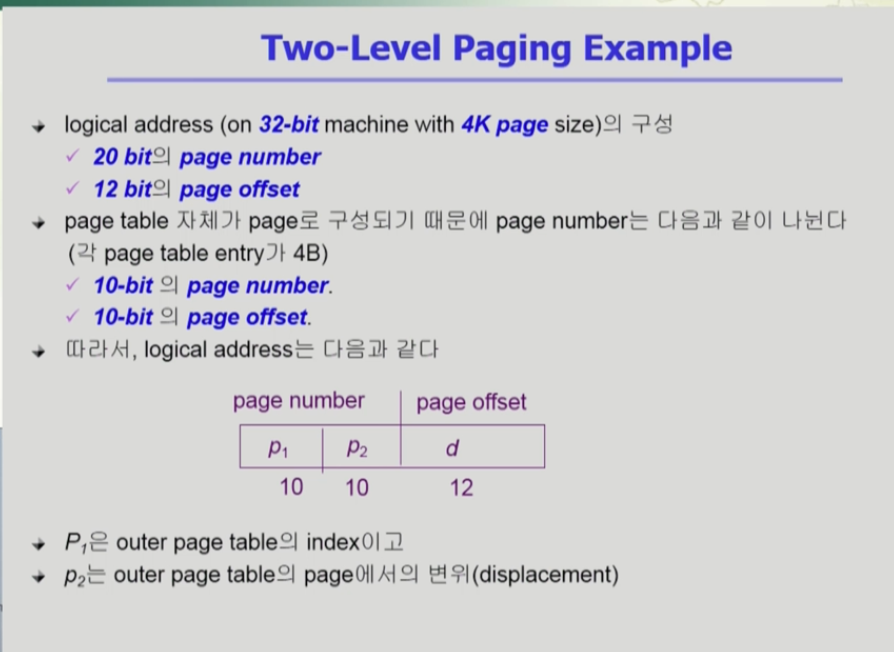

그래서 이런식으로 원래 페이지 offset은 당연히 있는거지만

바깥쪽 페이지테이블에는 어디에있고 내부 페이지테이블에서는 어디에있는지 정보를 가지고있어 경우의수를 늘리는것이다.

2단계 페이지 테이블에서의 변환은

논리적 주소에서 우선 바깥쪽 페이지 테이블에서 주소변환정보를 얻는다(안쪽페이지테이블이 어느페이지 테이블인지)

이제 안쪽 페이지테이블의 번호로 안쪽 페이지에서 물리적인 페이지 프레임을 찾는것이다.

여기서 알아야할것은 내부 페이지 테이블의 크기는 페이지의 크기와 같다.

37분부터 이제 내부에 바이트수가 어떻게 되는지 계산하는데 정리 부분에서는 생략한다 필요하면 다시 찾아가서 보자

대략 뭐어쩌구 저쩌구 해서 offset을 나타내는 비트는12비트이고 각 엔트리 구분용 페이지 테이블의 수는 10비트 씩이다 그래서 32비트가 된다 최종

페이지

'cs > 운영체제' 카테고리의 다른 글

| 20강 Memory Management 3 (1) | 2023.02.01 |

|---|---|

| 18강 Memory Management 1 (1) | 2023.01.30 |

| 17강 Deadlocks 2 (0) | 2023.01.24 |

| 16강 Deadlocks 1 (0) | 2023.01.24 |

| 15강 Process Synchronization 4(Concurrency Control) (0) | 2023.01.24 |